新書推薦: 《

梁衡给孩子的365堂作文课(孩子听得懂、学得进、用得上的大师级作文课)

》 售價:HK$

283.8

《

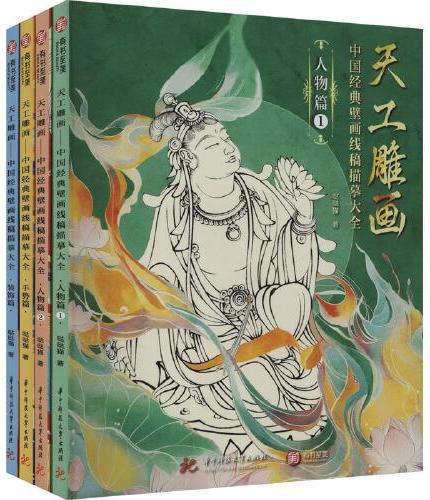

天工雕画:中国经典壁画线稿描摹大全(全4册)

》 售價:HK$

217.8

《

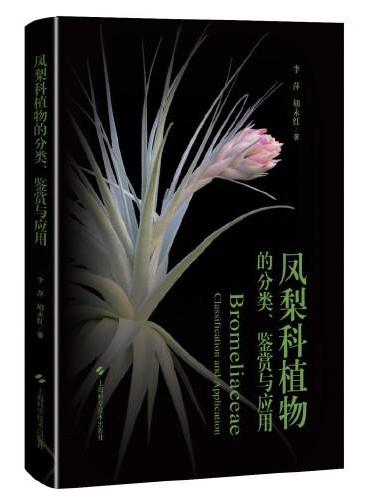

凤梨科植物的分类、鉴赏与应用

》 售價:HK$

492.8

《

《野草》意会

》 售價:HK$

107.8

《

格外的活法

》 售價:HK$

86.9

《

大陆银行(全两册)(上海市档案馆藏近代中国金融变迁档案史料续编(机构卷))

》 售價:HK$

624.8

《

断头王后:玛丽·安托奈特传(裸脊锁线版,德语直译新译本,内文附多张传主彩插)

》 售價:HK$

61.6

《

东南亚华人宗祠建筑艺术研究

》 售價:HK$

97.9

編輯推薦:

本书以项目开发为线索,系统地论述了FPGA项目设计的方法与实践,给出了丰富的设计实例。全书主要内容包括:? FPGA电子系统设计:总体方案、印制电路板、安装与调试、抗干扰与电磁兼容。? QUARTUSⅡ使用方法:编程、存储、编译、下载与仿真。? VHDL硬件描述语言:程序基本结构、语法、顺序描述语句、并行描述语句、 时钟信号描述与有限状态机设计。? FPGA数字电路设计方法与实例:门电路、组合逻辑电路、触发器与时序逻辑电路。? FPGA外围电路设计方法与实例:各类集成运算放大器典型电路、单电源供电的集成运算放大器的应用与集成运算放大器的综合应用。? FPGA小型数字系统项目设计实例:25个各类小型数字系统设计的案例。? FPGA综合数字系统项目设计实例:24个各类综合数字系统设计的案例。

內容簡介:

本书系统地论述了FPGA的设计方法,并给出了大量综合电子系统设计项目实例。全书共11章。第1章介绍FPGA电子系统的设计方法; 第2章介绍QuartusⅡ使用方法; 第3~7章介绍FPGA硬件描述语言VHDL的特点、VHDL语言中常用的数据、运算符、顺序描述语句和并行描述语句、时钟信号描述、有限状态机等基本概念和应用; 第8章介绍门电路、组合逻辑电路、触发器、时序逻辑电路(与阎石主编的《数字电子技术基础》(第4版)一致),并对其中的各种功能芯片以及基于VHDL与FPGA的实现方法进行了讲解; 第9章介绍FPGA外围电路集成运算放大器及其各种应用; 第10章和第11章给出了基于FPGA的综合电子系统设计实例。

目錄

目录

內容試閱

前言